### Nine Level Active Neutral Point Clamped (9L-ANPC) Inverter with Reduced Power Switches and DC-Link Voltage

### Harshitha K.P<sup>1</sup>, Dr. Shankaralingappa .C.B<sup>2</sup>

<sup>1</sup>M tech. Student (Power Electronics) Dr. Ambedkar Institute of Technology, Karnataka, India <sup>2</sup>Professor, Dept. of Electrical & Electronics Engineering, Dr. Ambedkar Institute of Technology, Karnataka, India \*\*\*

**Abstract** - This paper presents novel architecture of Nine level active neutral point clamped (9L-ANPC) inverter topology for medium-voltage high-power application using 8 active switches and 2 flying capacitor to minimize total harmonic Distortion. This unique arrangement of 9L-ANPC uses reduced number of passive and active components. DC link voltage is controlled by PWM technique. This 9L-ANPC configuration has reduced number of power switches & requirement of DC link voltage is 50%. The simulation of 9L-ANPC is carried out in MATLAB - Simulink. Results indicate nearly a sinusoidal voltage waveform with less Total Harmonic Distortion (THD) of 1.70%.

*Key Words*: Multi-level inverter (MLI), Active neutral point clamped inverter (ANPC), THD, Neutral point clamped converter (NPC), Flying Capacitor (FC) inverter.

#### **1. INTRODUCTION**

Presence of Harmonics in output sine waveform are major problem in power converter. In medium and small industrial applications, square waveform are used. Whereas ideal sinusoidal are preferred for large applications in industries but it is problematic to achieve less distorted sinusoidal wave due to presence of THD, it resembles as major problem in converter, these harmonics effects in overall efficiency of the system by drawing more current and heating of conductor results in failure of insulation and maintaining cost increases. Hence harmonics has to be reduced in sine wave as much as possible. Multilevel Inverter helps to overcome voltage limiting ability of semiconductor devises. MLI were introduced in late 1975 advancement in semiconductor helps in maintaining good power quality with reduced switching losses, yet there are still novel technologies coming up to discover in emerging zones of application which makes MLI,s more attractive[1]-[3].

These inverters proposals several advantages than Two-level converters (2L)which generate AC source with input of DC source generating 2 voltage levels  $+V_{dc}$ & -V<sub>dc</sub> across load with harmonics in output waveform. Classic multi-level inverter (MLI's) topologies includes flying capacitor inverter (FC), Neutral point clamped inverter (NPC) and CHB inverters are different types of MLI. Phase leg of 3L-NPC is easy to control with simple PWM technique, but it has unequal loss distribution between the semiconductors and difficulty of capacitor voltage balancing considered as major drawback [4]. Number of switches required in NPC is less but balancing of capacitor is a major problem [5] However Flying capacitor balances the load & distribute losses equally but controlling is difficult due to its increased number of capacitors [6]. New FCMI structure makes full DC input available by using low frequency two switches & generates double RMS which helps to increase amount of output but number of power switches used is more and THD is about 6.26% [7]. Author has combined 5 level ANPC inverter and HBBB to form nine level ANPC to obtain better quality of voltage and current waveform, advanced method of controlling is required and implementation is complicated[8]. In neutral point clamped T-type inverter a nine step voltage waveform are generated but the number of components used is more [9]. In this paper a seven level output voltage is generated using 8 power switches which uses PWM to control but THD is 2.7% [10]

#### 1.1 Demerits of conventional system

- There is a controlling complexity in flying capacitor inverter.

- Increases in switching loss and switching frequency in FC multilevel inverter.

- As level increases stage capacity also increases.

- For power conversion separate DC source are utilized in cascade inverter.

### 1.2 Merits of proposed system:

- Use of less active and passive elements.

- It has 4 capacitor with single DC sours as input.

- Easier and better control.

- Reduced number of component helps in improving system efficiency and reliability.

- Overall cost is less as compared to FC inverts and NPC inverters

### 2. Methodology

### 2.1 Analysis of proposed Topology

The typical MLI has come up with many problems when raising the level with THD. The NPC Multi-Level inverter becomes more complex as number of diodes increase with increasing output voltage steps, Flying Capacitor (FC) Multi-level inverter becomes expensive and heavy as requirement of capacitors increases.in case of Cascade-Multi-level inverter it requires variable voltage sources with increased voltage levels where as 9L-ANPC has only 8 switches hence switching losses is low & THD is reduced as output voltage level increases.

### 2.2 Block Diagram of 9L-ANPC using eight switches

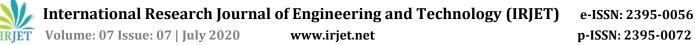

The novel nine level ANPC multilevel inverter consists of 8 power switches & 4 capacitors 2 of them are DC link capacitor and 2 are flying capacitor, this circuit is connected to grid as shown in Fig. 1.

Fig. 1. Block diagram of 9L-ANPC

In this the voltage measured from grid and theta is extracted from the grid voltage and based on the theta extracted, the modulation sine wave signal was generated so that the inverter voltage will be in phase to grid voltage.

# **2.3 Features of proposed novel 8 switch 9L-ANPC converter**

- Lesser number of active and passive components compare to other converters (FC, NPC etc.)

- Compared to conventional NPC, Cascade inverter and FC Inverter Families there is complete utilization of DC link Voltage.

- Voltage pressure on the switches is similar to the traditional inverter families such as NPC, Cascade inverter and Flying capacitor MLI, and individually power switch has a max voltage pressure of  $V_{dc}$ =  $V_{DC}/2$

- Size and ESR is reduced because DC-link capacitor voltage stress is about half.

### 3. Circuit Design & Description

9L-ANPC is a hybrid topology which combines inverter families of NPC, FC or Cascade H bridge multilevel inverter, all these methods uses more number of components which in turn increases total cost of the converter. This proposed topology designed with minimum number of switches.

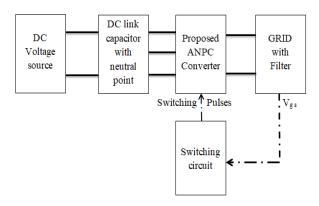

Fig. 2. Circuit Diagram of 9L-ANPC

The novel active neutral point clamped MLI of 9 level circuit is designed with four capacitors  $C_1, C_2, C_{F1}$  and  $C_{F2}$  and eight power switches namely  $S_{x1}, S_{x2}, S_{x3}, \dots, S_{x8}$  (where X is phase(R,Y,B)), switches used may be IGBT or MOSFET, Schematic of 9L-ANPC is shown in Fig.2 along with this switching signals circuits. In this eight switches  $S_{x3}, S_{x7}$  are Reverse blocking Insulated-Gate Bipolar Transistor (RB-IGBT) with series diode or it may be 2 MOSFETs with series Diode, and other switches  $S_{x1}, S_{x2}, S_{x4}, S_{x5}, S_{x6}$  are unipolar voltage devises with reverse conducting path such as 6 IGBT's / 6

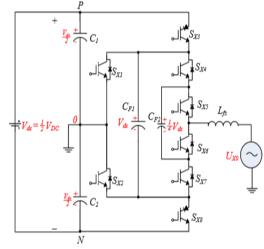

MOSFET', similar to 7L- ANPC [10],  $C_1$  and  $C_2$  are two series connected capacitors and their voltage is 1/2 of the DC link voltage and remaining six switches are  $S_{x1}$ ,  $S_{X4}$  and  $S_{X5}$  or  $S_{X2}$ ,  $S_{X6}$ ,  $S_{X7}$  Routes, which attached to AC terminal to the dc-link mid-point "0" as DC neutral point. The Flying Capacitor  $C_{F1}$  is charged by  $S_{X3}$  and  $S_{X8}$ at each switching cycle from the input  $V_{dc}$  to form a full simulated dc-bus of  $3^{rd}$  and  $4^{th}$  level (0.5V<sub>dc</sub> to 0.75V<sub>dc</sub> to  $V_{dc}$  or  $-0.5V_{dc}$  to  $-0.75V_{dc}$  to  $-V_{dc}$ ) voltage waveform at load side before the filter. Likewise, the charging of Flying Capacitor  $C_{F2}$  by  $S_{X3}$ ,  $S_{X4}$  and  $S_{X6}$  in the positive cycle and negative cycle through  $S_{X5}$ ,  $S_{X7}$  and  $S_{X8}$  to generate  $1^{st}\,and\,2^{nd}\,levels$  (0 to  $0.25V_{dc}\,or\,0$  to  $-0.25V_{dc}$ &  $0.25V_{dc}$  to  $0.5V_{dc}$  or -0.25Vdc to  $-0.5V_{dc}$ ). At ideal operation, the projected inverter has 9 output voltage levels:  $\pm V_{dc}$ ,  $\pm 3V_{dc}/4$ ,  $\pm V_{dc}/2$ ,  $\pm V_{dc}/4$ , 0 in positive & negative cycle and as reprasentated in Fig.3 and dclink voltage1is defined as  $V_{dc}$  for the proposed 9L-ABNPC, and, where  $V_{dc} = V_{DC} / 2$ .

Fig. 3. Nine output voltage levels

### **3.1 Switching Operation of Nine level Active Neutral point clamped Inverter**

Process of Active neutral point clamped inverter for power flow conversion from Direct current to Alternative current flow is explained using twelve Switching states as shown in Table-I which generates output of nine level voltage, using eight switches and four capacitor as detailed in circuit description. Each capacitor is maintained at DC link voltage of  $\frac{1}{2}V_{dc}$  and voltage of Flying capacitor  $C_{F1}$  and  $C_{F2}$  is  $V_{dc}$  and 0.25V<sub>dc</sub> respectively. Two switches  $S_{X1}$  and  $S_{X2}$  which are known as active switches are clamped to neutral point along with Capacitors  $C_1 \& C_2$  for equal voltage sharing between switches  $S_{X3}$ - $S_{X8}$  and helps to create switching states of Zero voltage.

The nine level ANPC inverter (9L-ANPC) switching table is shown in Table I:

| Table I: | Switching | states | of 9L | -ANPC: |

|----------|-----------|--------|-------|--------|

|----------|-----------|--------|-------|--------|

| State | Uxo                 | S <sub>x1</sub> | S <sub>x2</sub> | S <sub>x3</sub> | S <sub>x4</sub> | S <sub>x5</sub> | S <sub>x6</sub> | S <sub>x7</sub> | S <sub>x8</sub> |

|-------|---------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| А     | 0                   | 1               | 0               | 0               | 1               | 1               | 0               | 0               | 0               |

| В     | 0                   | 0               | 1               | 0               | 0               | 0               | 1               | 1               | 0               |

| С     | $1/4V_{DC}$         | 0               | 0               | 1               | 1               | 0               | 1               | 0               | 1               |

| D     | 1/4V <sub>DC</sub>  | 0               | 1               | 0               | 0               | 1               | 0               | 1               | 0               |

| Е     | 1/2V <sub>DC</sub>  | 0               | 0               | 1               | 1               | 1               | 0               | 0               | 0               |

| F     | 3/4V <sub>DC</sub>  | 0               | 1               | 0               | 1               | 0               | 1               | 0               | 0               |

| G     | Vdc                 | 0               | 1               | 0               | 1               | 1               | 0               | 0               | 0               |

| Н     | -1/4VDC             | 0               | 0               | 1               | 0               | 1               | 0               | 1               | 1               |

| Ι     | -1/4VDC             | 1               | 0               | 0               | 1               | 0               | 1               | 0               | 0               |

| J     | -1/2V <sub>DC</sub> | 0               | 0               | 1               | 0               | 0               | 1               | 1               | 1               |

| К     | -3/4V <sub>DC</sub> | 1               | 0               | 0               | 0               | 1               | 0               | 1               | 0               |

| L     | -VDC                | 1               | 0               | 0               | 0               | 0               | 1               | 1               | 0               |

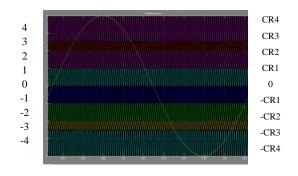

The PWM technique is used for the proposed 9L-ANPC inverter which uses all 12 switching states to produce the appropriate voltage level at inverter output as shown in Fig.4 and compared with single modulation  $V_{ref}$  voltage with 4 carrier wave for positive cycle & remaining 4 carrier waves for negative cycle CR1, CR2, CR3, CR4 and -CR1, -CR2, -CR3, -CR4 respectively.

Fig. 4. The pulse width modulation (PWM) for 9L-ANPC

#### **4. SIMULATION RESULT**

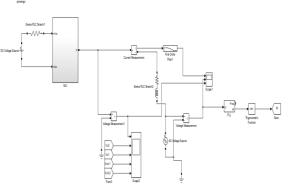

Operation of 9L-ANPC is performed using MATLAB-SIMULINK by taking a component parameters as shown in Table-II. 9L-ANPC is simulated as shown in Fig.5 with input of 400V DC supply to get output voltage of 230V which is filtered to obtain nearly sinusoidal wave of 230V  $V_{\text{ph}}$  and current of 10A at load for both R and RL load.

## **Table II:** Components and parameters used forSimulation

| Parameters                           | Value         |  |  |  |  |

|--------------------------------------|---------------|--|--|--|--|

| Input voltage(V <sub>dc</sub> )      | 400V          |  |  |  |  |

| Output voltage (V <sub>ac</sub> )    | 230V          |  |  |  |  |

| Power rating(P <sub>o</sub> )        | 2.2 kVA       |  |  |  |  |

| Dc-link capacitor ( $C_1 \& C_2$ )   | 10 mF,200V    |  |  |  |  |

| Flying capacitor (C <sub>FC1</sub> ) | 10 mF,400V    |  |  |  |  |

| Flying capacitor ( $C_{FC2}$ )       | 10 mF,100V    |  |  |  |  |

| Carrier frequency (f <sub>s</sub> )  | 5 kHz         |  |  |  |  |

| Line frequency(f)                    | 50 Hz         |  |  |  |  |

| Load (RL)                            | 20Ω and 200mH |  |  |  |  |

Oscela. Is= 1e06 s

Fig.5. 9L-ANPC in Mat lab

The proposed converter consists of 8 switches and two flying capacitors and two input capacitors with neutral midpoint. The pulses will be provided with the help of switching circuit based on the switching Table II.

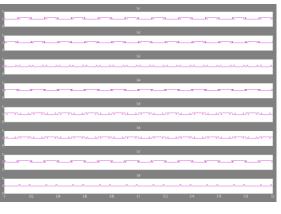

The switching pulses for eight switches nine level inverter is shown in Fig.6:

Fig.6. Switching pulses for 8 switch

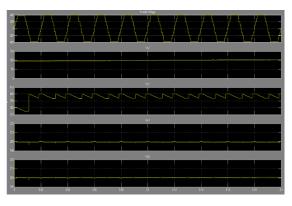

Fig.7 represents the output voltage level & capacitor voltage waveforms of 9L-ANPC

Fig. 7. Capacitor  $C_{F1}$  &  $C_{F2}$  waveforms of 9L-ANPC for RL load

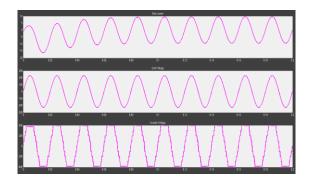

The output of grid voltage, Grid current waveforms and 9 steps of 9L-ANPC for RL load are shown below in Fig.8.

Fig.8. Voltage & Current Output of 9L-ANPC for RL load

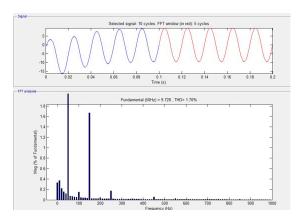

The Total harmonic distortion for RL load is shown below in Fig.9:

Fig. 9. THD of 9L-ANPC

Total harmonic distortion of proposed 9L-ANPC for RL load is 1.70% which is less than 7L-ANPC inverter with THD of 2.4% [10].

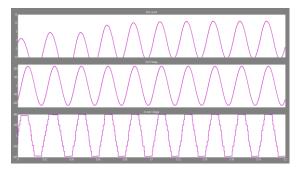

The grid voltage, current waveforms and 9 steps of 9L-ANPC for R load is shown in Fig.10 following graphs:

Fig. 10. Voltage & Current Output of 9L-ANPC for R load

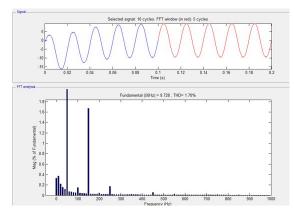

The Total harmonic distortion (THD) for R load is shown in Fig.11:

Fig. 11. THD of 9L-ANPC

Total harmonic distortion of proposed 9L-ANPC inverter for R load is 1.70%. THD for both R and RL load is same.

### **5. CONCLUSION**

In this paper a new nine level active neutral point clamped (9L-ANPC) inverter is proposed with analysis of THD using only 8 power switches for single phase (230V) with reduced Dc-link voltage to generate sinusoidal wave of 1.70% THD at load side, which improves over-all efficiency of the system and reduces the total cost of the inverter due to reduced number of power switches.

### REFERENCES

- [1] S. Kouro, M. Malinowski<sub>1</sub>, K. Gopakumar<sub>2</sub>, J. Pou<sub>3</sub>, L. G. Franquelo<sub>4</sub>, B. Wu, J. Rodriguez<sub>5</sub>, M. A. Perez<sub>6</sub>, and J. I. Leon, "Recent Advances and Industrial Applications of Multilevel Converters," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2553-2580, Aug. 2010.

- [2] J. Rodríguez , J. S. Lai , and F. Z. Peng , "Multilevel Inverters: A Survey of Topologies, Controls, and Applications," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724-738, Aug. 2002.

- [3]Jose Rodriguez, Senior Member, IEEE, Steffen Bernet, Member, IEEE, Peter K. Steimer, Fellow, IEEE, and Ignacio E. Lizama "A Survey on Neutral-Point-Clamped Inverters" IEEE Transactions on industrial electronics, vol. 57, no. 7, july2010 2219

- [4] Gandla Radha Krishna, K. Anuradha "Neutral Point Voltage Level Stabilization and DC Link Capacitors Voltage Balance in Neutral Point Clamped Multilevel Inverters" IEEE international conference on industrial and information system

- **[5]**C. Feng, J. Liang, and V. Agelidis, "Modified Phase-Shifted PWM Control for Flying Capacitor Multilevel Converters," IEEE Trans. Power Electron, vol. 22, no. 1, pp. 178-185, Jan. 2007.

- [6] Dhivya.K, Mahes Kumar.V, Babu.E "A Novel Flying Capacitor Multilevel Inverter with Stable Output Voltage" in IJRP Volume 1 Issue 6, December 2017

- [7] M.Nagaraju1, D.Ravikiran2 "Comparative Analysis of Nine Level Inverter with Two Different

Topologies" in IJAREEIE Vol. 5, Issue 12, December 2016

- [8] Jun Li, Student Member, IEEE, Subhashish Bhattacharya, Member, IEEE, and Alex Q. Huang "A New Nine-Level Active NPC (ANPC) Converter for Grid Connection of Large Wind Turbines for Distributed Generation" IEEE Transactions On Power Electronics, Vol. 26, No. 3, March 2011

- **[9]** Teenu Techela Davis, Anubrata Dey "Nine Level Ttype Neutral Point Clamped Voltage Source Inverter for Induction Motor Drive" 43rd Annual Conference of the IEEE Industrial Electronics Society, 18 December 2017.

- [10] Yam P. Siwakoti , Member, IEEE, Akshay Mahajan, IEEE, Dan Rogers, Member, IEEE, Frede Blaabjerg, Fellow, IEEE "A Novel Seven-Level Active Neutral Point Clamped Converter with Reduced Active Switching Devices and DC-link Voltage".2018